Background

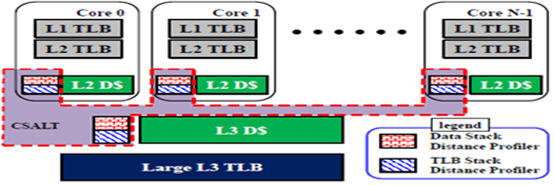

Context Switch Aware Large TLB (CSALT) addresses the problem of increased TLB miss rates and their adverse impact on data caches. The invention proposes to partition the on-chip caches to house translation entries (TLB entries/page table entries) alongside data. The partitioning is achieved by means of a low overhead cache partitioning algorithm which allocates capacity for translation entries depending on the demand. CSALT architecture can effectively cope with the demands of increased context switches by its capacity to store a very large number of TLB entries.

Features

- An architecture which utilizes low overhead cache partitioning algorithm to allocate optimal cache capacity for translation entries housed alongside the data in on-chip data caches.

- Majority of the page walk latency is replaced with access latency of an on-chip data cache.

Benefits

- CSALT provides 85% improvement over systems employing a conventional L1/L2 TLBs of 8-core configurations running PARSEC and Graph workloads.

- CSALT provides 25% improvement over systems employing a large L3 TLB.

IP Status: US Patent Grant 10,261,915

Fig.1: CSALT System Architecture.