Background

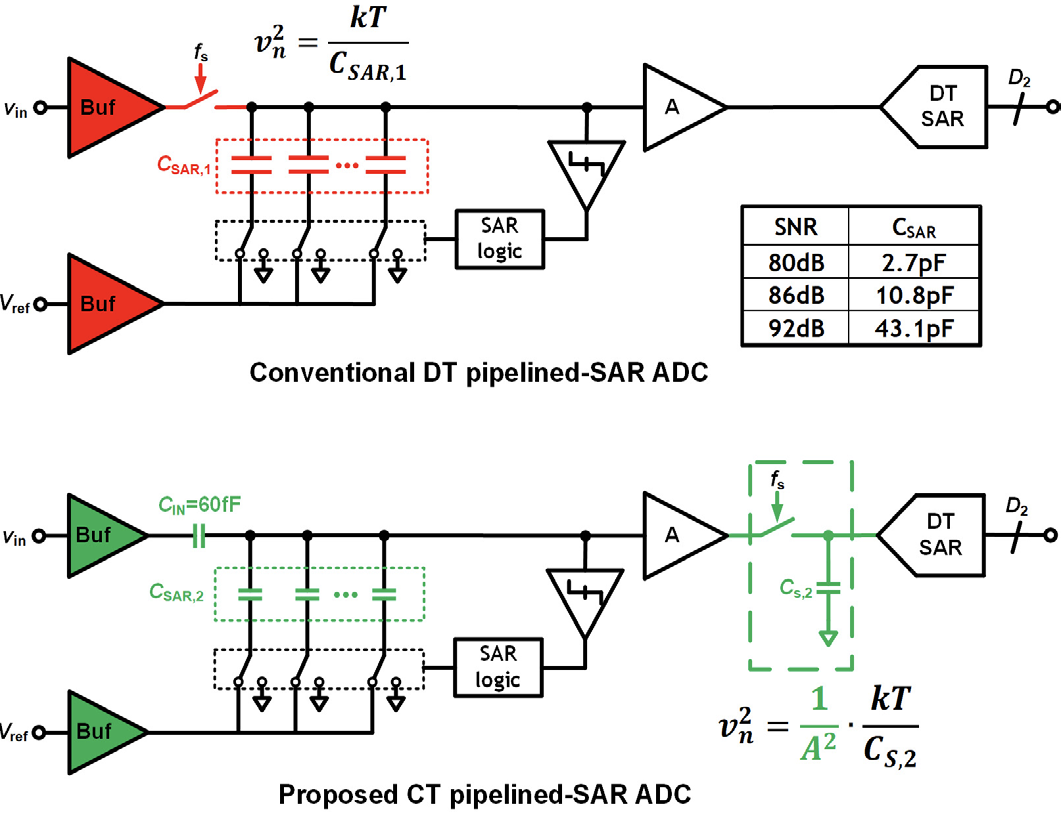

The kT/C noise poses a fundamental signal to noise ratio (SNR) limit for discrete-time (DT) analog to digital converters (ADCs) with the front-end sampling operation. To achieve a high resolution, the sampling capacitor needs to be sufficiently large (e.g., 3pF for 80-dB SNR assuming 2Vpp swing) and it has to be quadrupled for every 1-bit increase in the resolution. A large sampling capacitor poses critical challenges for both the ADC input buffer and the reference buffer (Fig. 1). To meet the stringent linearity requirement of high-resolution ADCs, these buffers consume a significant amount of power, which can be comparable or even higher than the ADC itself. In addition, a large capacitor makes it difficult to design the ADC front-end sample and hold circuit, leading to considerable power/area costs and increased design complexity.

Technology description

Researchers at The University of Texas at Austin have developed a 13-bit pipelined-SAR ADC with a continuous-time (CT) input stage that is kT/C noise free (Fig. 1). Hence, the first-stage capacitor size is not bounded by the kT/C limit and can be significantly reduced. Unlike a classic pipelined-SAR ADC, the sampling operation is moved to the second stage. Hence, the kT/C noise from the second-stage is suppressed by the first-stage gain, making possible the use of a small sampling capacitor in the second-stage too. In the prototype ADC, the first-stage input capacitor is only 120fF (60fF single-ended), which is 25x smaller than 3pF (set by kT/C noise limit) in a classic DT pipelined-SAR ADC of the same resolution. This substantially smaller capacitor size reduces the chip area. Moreover, it greatly relaxes the performance requirement of the ADC input buffer and the reference buffer, leading to significant power saving on the system level.

Results

The technology with same resolution, the proposed continuous-time SAR ADC reduces the sampling capacitor by at least 10× and overall chip area by at least 5×, compared with conventional SAR ADC. Further discussion of the technology can be found here.

- The SAR is kT/C noise free, and the capacitor required can be significantly reduced to be below than the theoretical limitation.

- The small capacitor DAC relaxes input driver and reference buffer, saving the overall driving power and reference power by at least one order of magnitude.

- The proposed SAR ADC uses capacitive feedback, which is noise-less, and less power-hungry, compared with the resistive input and IDAC feedback.

- The dynamic amplifier is output-common-mode voltage stable and shows great common-mode rejection.

Figure 1. Comparison of the conventional SAR ADC to the proposed.