Background

Delta-Sigma fractional-N PLL plays an important role in modern electronic systems. Unlike integer-N PLLs, fractional-N PLLs allow synthesis of frequencies that are a fraction of the reference frequency. Thus, a fractional-N PLL can use a higher reference frequency than an integer-N PLL for the same frequency resolution. It allows a wider PLL bandwidth, leading to faster settling time and stronger suppression of VCO noise. However, Delta-Sigma fractional-N PLLs have an additional noise source: quantization noise from the Delta-Sigma modulator used to generate the fractional division ratio. For a wide-band PLL, the quantization noise can easily dominate the PLL phase noise.

There have been several approaches to address this issue. An analog approach is to inject current into the charge pump to cancel out the instantaneous phase error due to Delta-Sigma quantization noise. However, this approach requires a very high resolution digital-to-analog converter (DAC) along with accurate gain and offset calibration techniques. A multi-phase ring VCO can be used to cancel the instantaneous phase error, but it requires complicated phase realignment technique. Another mostly digital approach is to use an FIR filter at the output of the 1-bit Delta-Sigma modulator to reduce the quantization noise, but it is effective only at high frequencies. For a wide-band PLL, a large number of FIR filter taps are required to adequately suppress the quantization noise.

Results

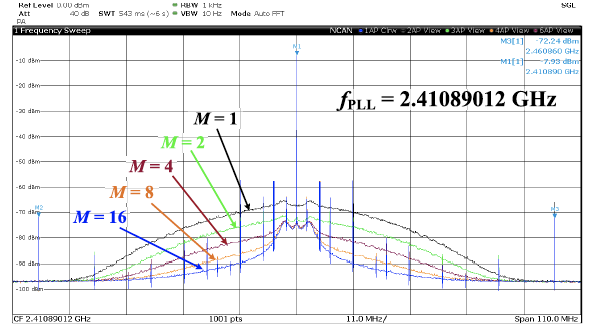

Researchers at The University of Texas at Austin have developed a technique that shows a simple, effective, and mostly digital technique to reduce the Delta-Sigma quantization noise at all frequencies. It is based on a new concept of spatial averaging, which is realized by using an array of dividers, phase/ frequency detectors (PFDs), and charge pumps (CPs). The new architecture employs an array-like vector divider, vector phase/frequency detector (VPFD) and vector charge pump (VCP), composed of M identical copies of corresponding elements, to achieve spacial averaging.

The proposed technique achieves a significant improvement in performance over the conventional technique and the FIR filtering technique while incurring only a small increase in hardware complexity. A prototype 2.4-GHz fractional-N PLL is implemented in a 40nm CMOS process. Measurement results show that the in-band and out-of-band noise are reduced by 8dB and 20dB, respectively. The performance summary, comparison to other techniques, and block diagrams may be found in the published documents here and here.

Figure 1: Measured output spectra at the fractional -N modes with different M values.